Basic Computer Organization and Design

0

# **Computer Organization**

- Organization of computer is defined by:

- Internal Registers

- Timing and Control Structure

- Set of Instructions

- Internal Organization of digital system is defined by the sequence of microoperations it performs on data stored in registers

- General Purpose Computer is capable of

- Executing various microoperations

- It can be instructed as to what specific sequence of operations it perform

- User of a computer can control the process by means of a program

- Program is a set of instructions that specify the operations, operands and sequence by which processing has to occur

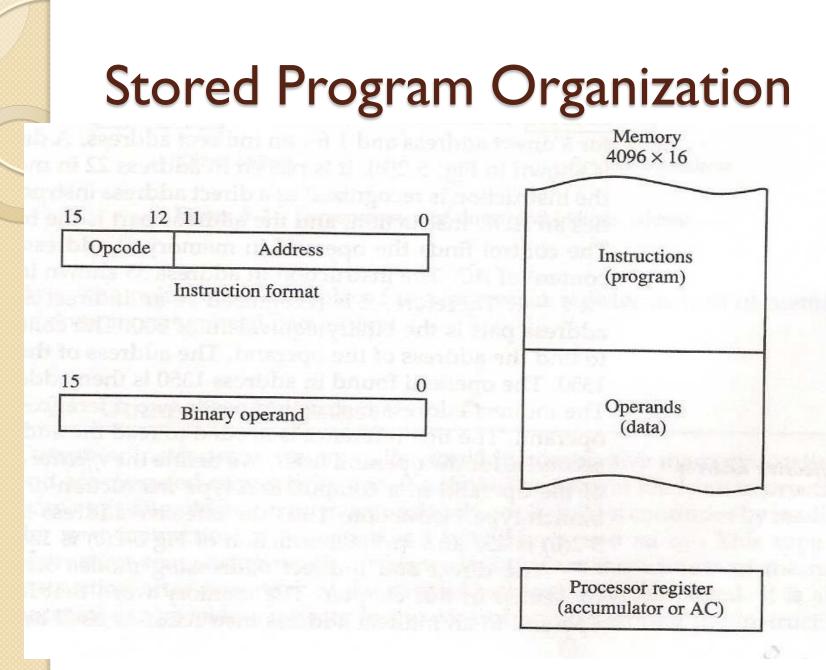

- A computer instruction is a binary code that specifies a sequence of microoperations for the computer

- Instruction code together with data are stored in memory

- Computer reads each instruction from memory and places it in control registers

- Control then interprets the binary code of the instruction and proceeds to execute it by issuing a sequence of microoperations

- Every computer has its own unique instruction set

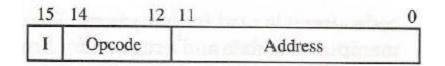

- An Instruction code is group of binary bits that instruct the computer to perform a specific operation

- It is usually divided into parts, the most basic is operation part

- The operation code of an instruction is a group of bits that define operations such as ADD,MUL,SUB

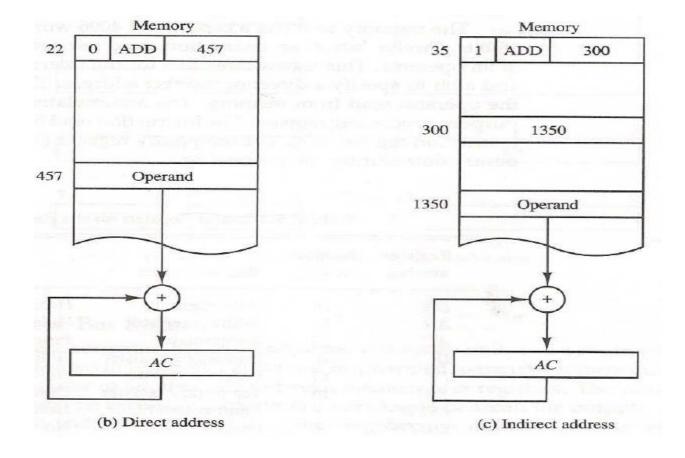

#### Indirect Address

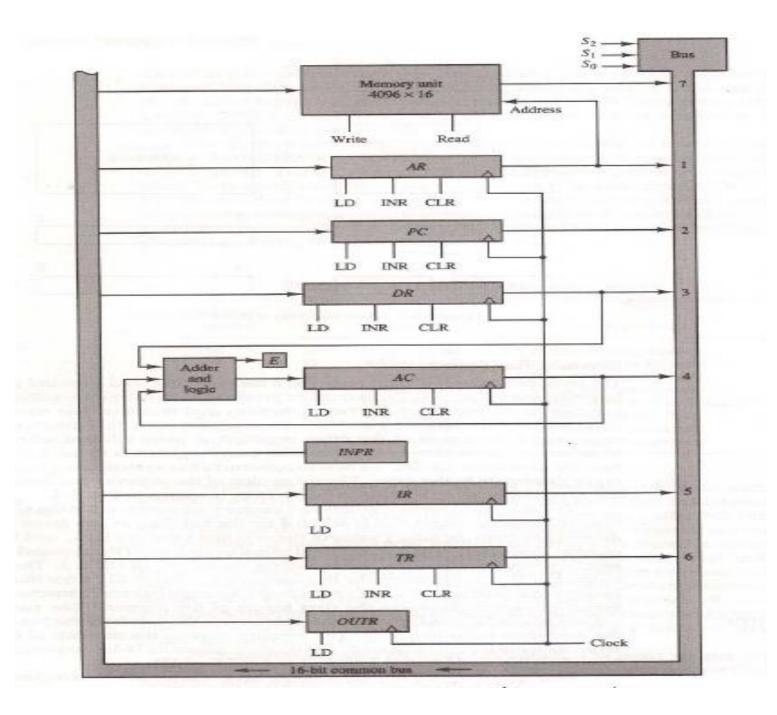

#### List Of Registers in Basic Computer

| Register<br>symbol | Number<br>of bits | Register name                           | Function               |  |

|--------------------|-------------------|-----------------------------------------|------------------------|--|

| DR                 | 16                | Data register                           | Holds memory operand   |  |

| AR                 | 12                | Address register Holds address for me   |                        |  |

| AC                 | 16                | Accumulator                             | Processor register     |  |

| IR                 | 16                | Instruction register                    | Holds instruction code |  |

| PC                 | 12                | Program counter Holds address of instru |                        |  |

| TR                 | 16                | Temporary register Holds temporary data |                        |  |

| INPR               | 8                 | Input register Holds input character    |                        |  |

| OUTR               | 8                 | Output register Holds output character  |                        |  |

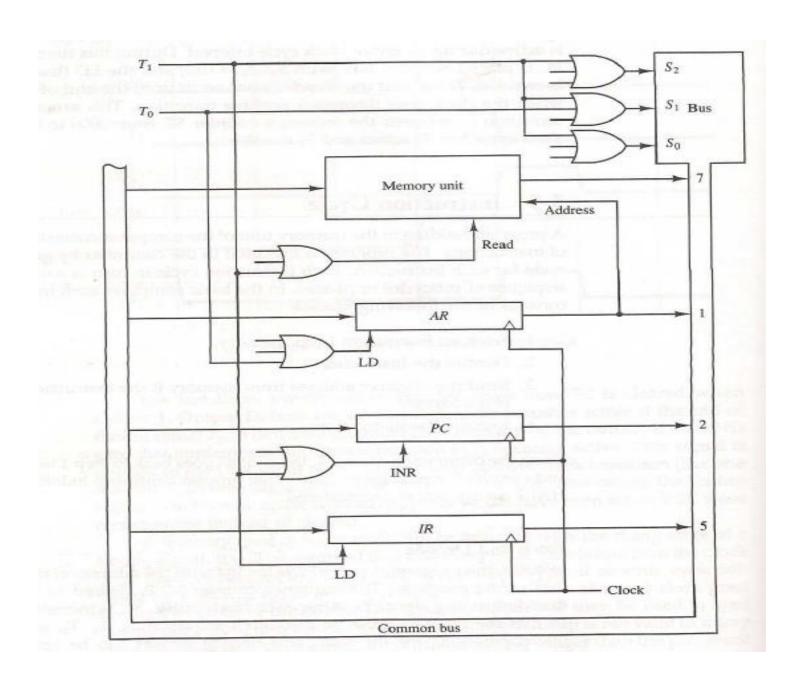

### **Common Bus System**

- Basic computer has 8 registers, control unit and a memory unit

- Paths must be provided to transfer information from one register to another and between memory and registers

- Lots of wires will be required to connect output of each registers to the input of each register

- An efficient scheme is needed to transfer of information

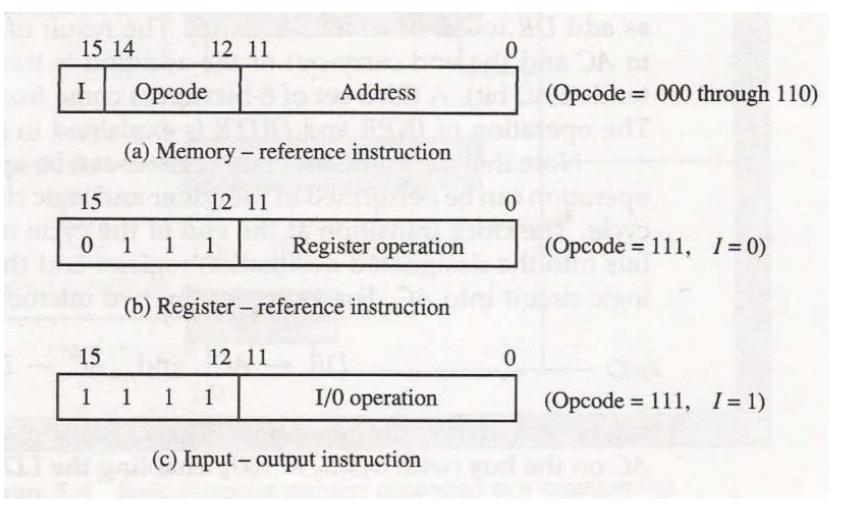

#### **Computer Instructions**

#### **Basic Computer Instructions**

|        | Hexadecimal code |      | a thorn. The branch bestry store 1   |  |

|--------|------------------|------|--------------------------------------|--|

| Symbol | I = 0 $I = 1$    |      | Description                          |  |

| AND    | Oxxx             | 8xxx | AND memory word to AC                |  |

| ADD    | 1xxx             | 9xxx | Add memory word to AC                |  |

| LDA    | 2xxx             | Axxx | Load memory word to AC               |  |

| STA    | 3xxx             | Bxxx | Store content of AC in memory        |  |

| BUN    | 4xxx             | Cxxx | Branch unconditionally               |  |

| BSA    | 5xxx             | Dxxx | Branch and save return address       |  |

| ISZ    | 6xxx             | Exxx | Increment and skip if zero           |  |

| CLA    | 7800             |      | Clear AC                             |  |

| CLE    | 7400             |      | Clear E                              |  |

| CMA    | 7200             |      | Complement AC                        |  |

| CME    | 7100             |      | Complement E                         |  |

| CIR    | 7080             |      | Circulate right AC and E             |  |

| CIL    | 7040             |      | Circulate left AC and E              |  |

| INC    | 7020             |      | Increment AC                         |  |

| SPA    | 7010             |      | Skip next instruction if AC positive |  |

| SNA    | 7008             |      | Skip next instruction if AC negative |  |

| SZA    | 7004             |      | Skip next instruction if AC zero     |  |

| SZE    | 7002             |      | Skip next instruction if $E$ is 0    |  |

| HLT    | 7001             |      | Halt computer                        |  |

| INP    | F800             |      | Input character to AC                |  |

| OUT    | F400             |      | Output character from AC             |  |

| SKI    | F200             |      | Skip on input flag                   |  |

| SKO    | F100             |      | Skip on output flag                  |  |

| ION    | F080             |      | Interrupt on                         |  |

| IOF    | F040             |      | Interrupt off                        |  |

# What type of instructions be included?

- A computer should have a set of instructions so that the user can construct machine language programs to evaluate any function that is computable

- Set of instructions are said to be complete if computer have sufficient number of instructions in the following categories:

- Arithmetic, Logical and Shift instructions

- Instructions for moving information to and from memory and processor registers

- Program control instructions to check status conditions

- Input and Output instructions

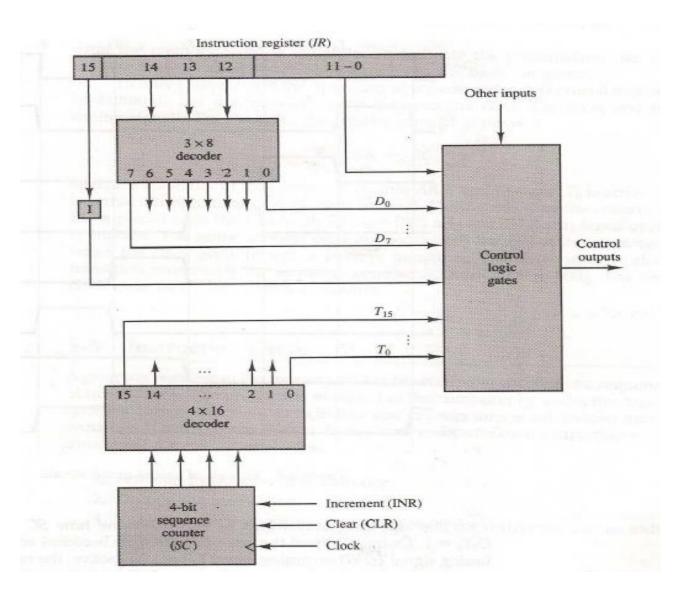

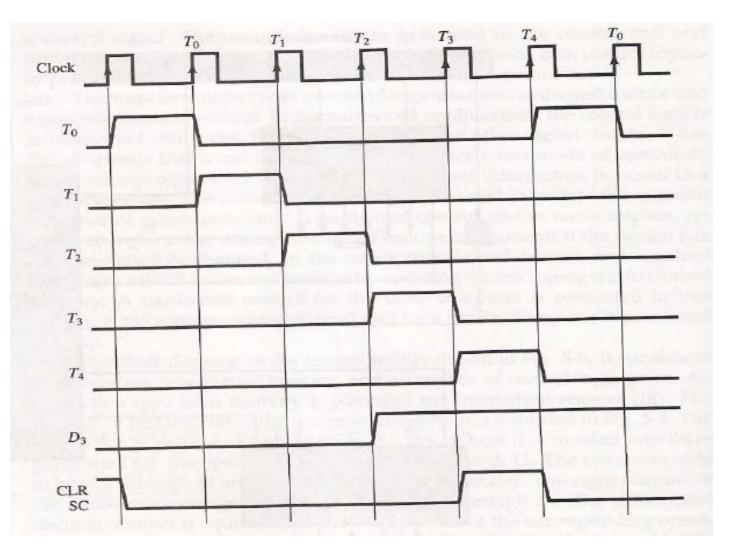

# **Timing and Control**

- Timings in basic computer is generated by master clock generator

- Clock Pulses are applied to all flip flops and registers in the system including those in the control unit

- Clock Pulses do not change the state of register unless the register is enabled by the control signal

- Control signals are generated in the control unit and provide control inputs for the multiplexers in the common bus, control inputs in processor registers and microoperations for the control input

- Two major types of control organization

- Hardwired Control

- Micro programmed Control

- Basic control unit for Hardwired Control organization consists of

- Two decoders

- Sequence Counter

- No. of control logic gates

$D_3T_4: SC - 0$

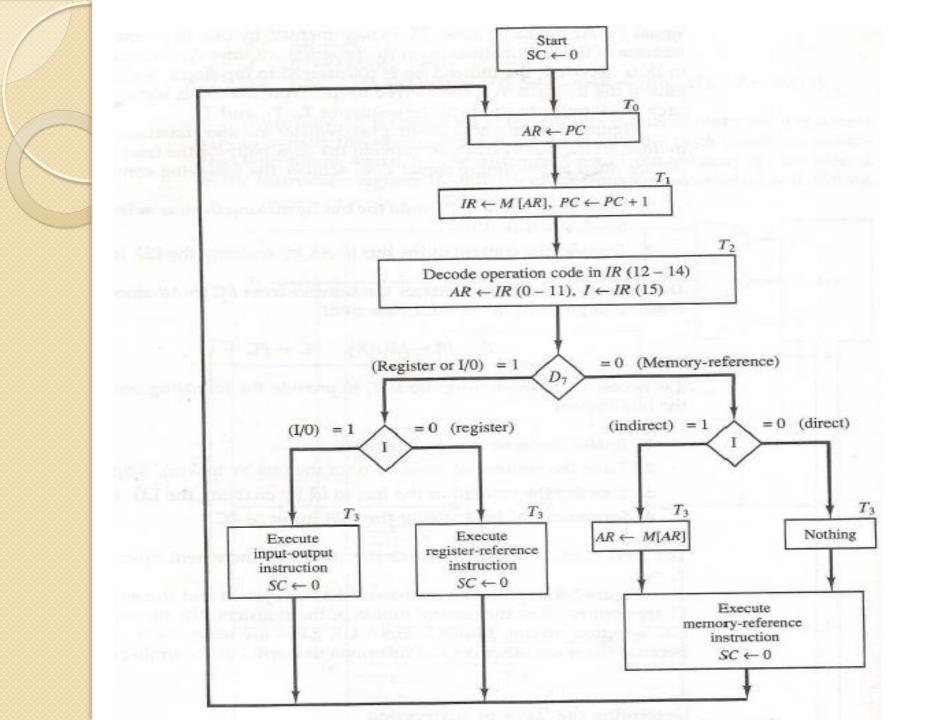

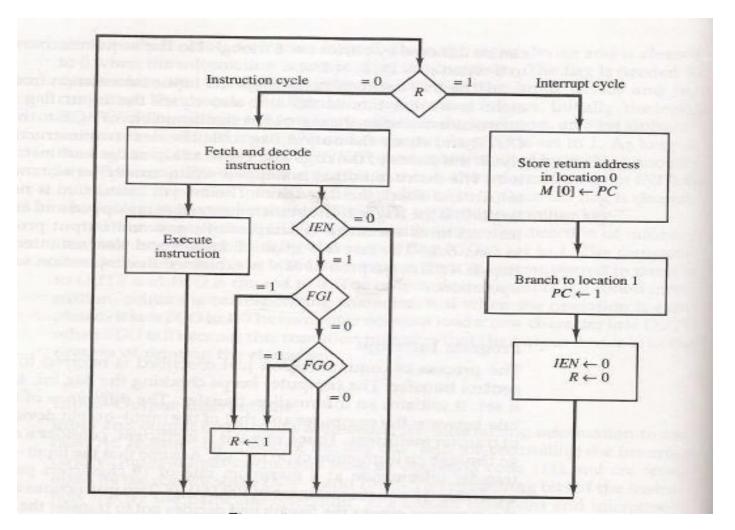

# Instruction Cycle

- Program residing in the memory unit of computers contains sequence of instructions

- Program is executed in computer by going through a cycle for each instruction

- Each instruction cycle is sub divided into different sub cycles or phases

- In basic computer each instruction cycle consists of :

- Fetch an instruction from memory

- Decode the instruction

- Read the effective address from the memory if instruction has indirect address

- Execute the instruction

#### Fetch & Decode

- Initially, the program counter PC is loaded with address of the first instruction

- SC is cleared to 0 to decode  $T_0$

- Microoperations for fetch and decode phase can be specified by following register statements:

```

T_0: AR \leftarrow PC

```

```

T_1: IR \leftarrow M[AR], PC \leftarrow PC + 1

```

$T_2: D_0, \ldots, D_7 \leftarrow \text{Decode } IR(12-14), AR \leftarrow IR(0-11), I \leftarrow IR(15)$

- To provide the data path for the transfer of PC to AR we must apply timing signal  $T_0$  achieve the following:

- Place the content of PC onto the bus by making the bus selection inputs S<sub>2</sub>S<sub>1</sub>S<sub>0</sub> equal to 010

- Transfer the content of bus to AR by enabling the LD input of AR

- Then, next clock transition initiates the transfer of PC to AR since  $T_0 = I$

• To implement the next statement it is necessary to use timing signal  $T_1$  to provide the following connections in the bus system

Enable the read input of memory

- $^{\circ}\,$  Place the content of memory onto bus by making  $S_{2}S_{1}S_{0}$  equal to 111

- Transfer the content of the bus to IR by enabling the LD input of IR

- Increment the PC by enabling the INR input of PC

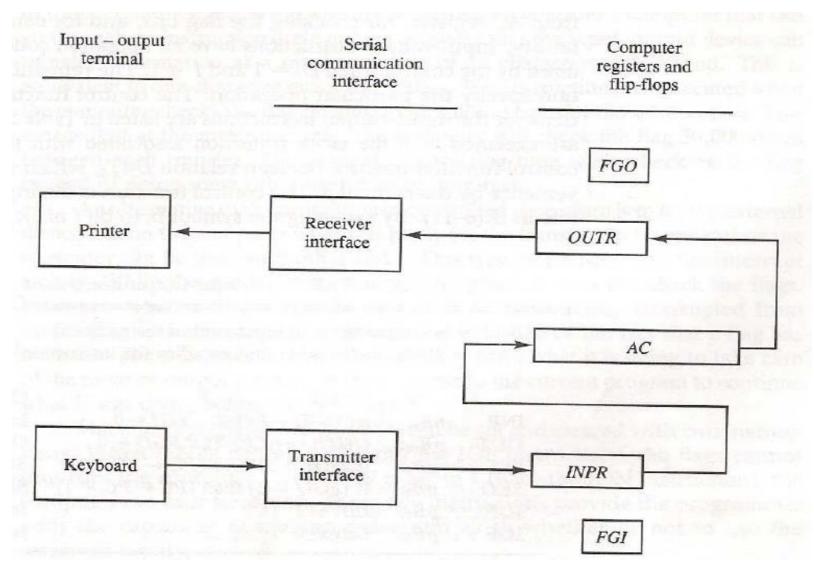

# I/O Configuration

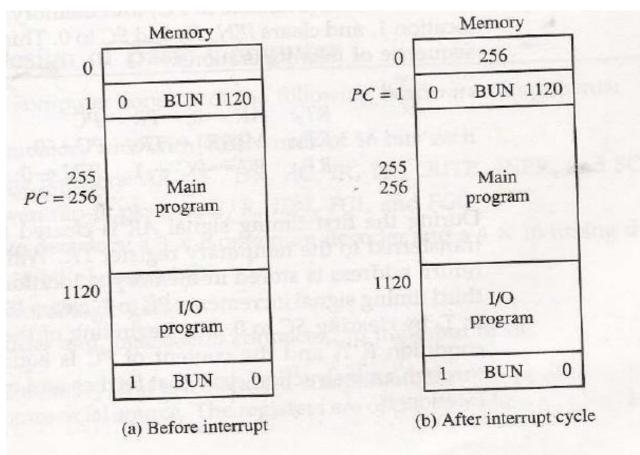

#### Program Interrupt

- The process of communication just discussed is referred to as programmed control transfer

- Computer keeps checking the flag bits, and if set, it initiates information transfer

- Difference of information flow rate between computer and that of I/O device makes this type of transfer inefficient

- Why???

Consider a computer with instruction cycle time 1µs and 1/O device can transfer information at a rate of 10 characters/sec

° i.e I character every 100,000 μs

- Two instructions are executed when computer checks the flag bit and decides not to transfer information

- i.e At max rate the computer will check the flag 50,000 times between each transfer

- Computer is wasting time while checking the flag instead of doing some other useful processing task

- Alternative to the programmed controlled procedure is to let the external device inform the computer when it is ready for transfer

- This type of transfer uses the interrupt facility

- IEN flip-flop helps to interrupt the processing of a computer program

- IEN=0, the interrupt cannot be made

- IEN=I, the interrupt can be made

## Flowchart of Interrupt Cycle

#### Interrupt cycle is h/w implementation of branch and save return address